阻抗偏差解决方案

阻抗偏差超过±10%时,需重新计算线宽并检查蚀刻均匀性。推荐使用线宽补偿算法,结合在线蚀刻速率监测,将偏差控制在±5%以内。对于高频板,建议使用介电常数稳定的材料(如RogersRO4003C)。检测方法:使用TDR时域反射仪分段测量,定位阻抗异常区域。某企业通过该方法,将阻抗合格率从85%提升至98%。预防措施:定期维护蚀刻设备,确保药液浓度(HCl5-8%,FeCl338-42%)与温度(45-50℃)稳定。工艺改进:采用脉冲蚀刻技术,蚀刻均匀性提升至±3%,适合精细线路加工。 43. 阻抗偏差超过 ±10% 需重新计算线宽,检查蚀刻均匀性。上海打样PCB厂家报价

云平台协同设计与知识产权保护

云平台协同设计支持多人实时编辑,自动检测。设计文件通过区块链存证,确保知识产权保护,版本追溯精度达分钟级。支持Gerber、BOM等文件在线预览,无需本地安装设计工具。技术架构:①分布式版本控制(Git);②权限分级管理;③数据加密传输(AES-256)。客户价值:某设计公司通过云平台,异地协作效率提升50%,设计文件泄露风险降低90%。商业模型:按用户数或项目收费,提供基础版(5用户)、专业版(20用户)等套餐。 广东打样PCB厂家电话17. 阻抗测试频率选择 1-10GHz,确保覆盖信号带宽。

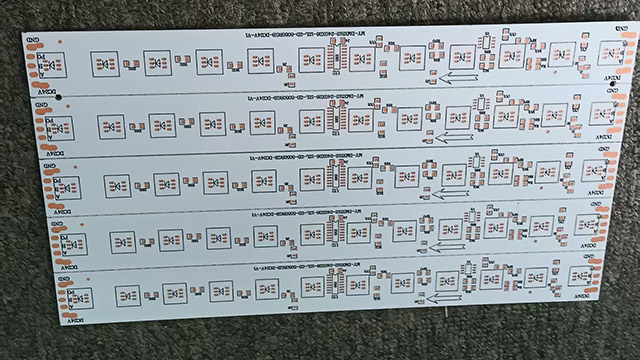

PCB元件封装设计优化

PCB元件封装设计需严格遵循IPC-7351标准,焊盘尺寸需与元件管脚匹配。以0402封装电阻为例,焊盘长度±、宽度±,降低墓碑效应风险。对于QFP封装,引脚间距≤,边缘粗糙度Ra≤μm,避免桥接缺陷。工艺要点:焊盘设计需预留,阻焊层开窗比焊盘大。推荐使用AltiumDesigner的封装库管理器,自动生成符合IPC标准的焊盘,并通过3D模型验证空间干涉。数据支持:某企业通过优化0603封装电容焊盘,使焊接良率从,返修成本降低40%。对于BGA封装,采用焊盘优化算法可减少。失效分析:焊盘设计不当易导致焊接时焊锡量不足,建议使用J-STD-001标准计算焊盘面积。以,焊盘直径,焊锡体积需达到³/球。

2025年PCB技术发展趋势

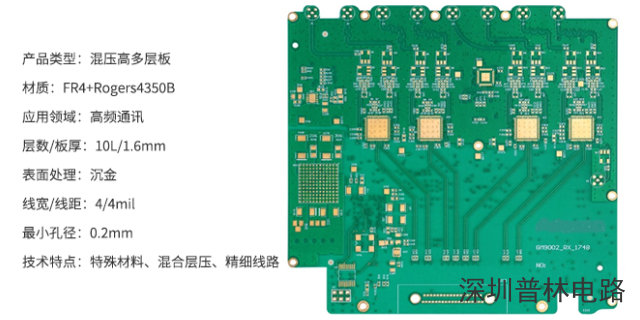

2025年PCB技术趋势包括:100Gbps高速传输、20层以上HDI板、Chiplet基板规模化应用。线宽/间距突破1μm,采用极紫外光刻技术实现更高集成度。环保材料占比超60%,无卤、可降解基材成为主流。关键技术:①3D封装(TSV硅通孔);②激光直接成像(LDI);③增材制造(AM)。市场预测:据Prismark数据,2025年全球PCB市场规模将达950亿美元,其中高阶HDI板占比超30%。企业策略:加大研发投入,布局先进封装、智能生产等技术,建立绿色供应链体系。 12. 铣边加工残留铜屑需≤0.05mm,采用高压水刀清洗工艺。

选择性焊接技术(SelectiveSoldering)

选择性焊接技术采用氮气保护,减少助焊剂残留。通过编程控制焊接时间(3-5秒)与温度(260℃±5℃),确保通孔元件焊接合格率>99.9%。适用于混装板(SMT+THT),可替代波峰焊减少锡渣产生。设备参数:①喷头精度±0.1mm;②氮气流量5-10L/min;③焊接压力0.5-1.0N。成本分析:相比波峰焊,选择性焊接可节省助焊剂70%,能耗降低40%,适合小批量、高混合度生产。工艺优化:采用双波峰焊接技术,提升焊接质量,减少桥接缺陷。 44. 焊盘不上锡可能由 OSP 膜过厚或焊接温度不足导致。上海打样PCB厂家报价

0603 封装电容焊盘间距建议 0.5mm,避免回流焊时出现墓碑效应。上海打样PCB厂家报价

未来PCB技术挑战与机遇

未来PCB面临的挑战包括:更高集成度(如Chiplet)、更低功耗(如量子计算)、更严格环保要求(如可降解材料)。机遇在于新能源汽车、AI服务器、6G通信等新兴领域的需求增长。企业需加大研发投入,布局先进封装、智能生产等技术。战略建议:①建立联合实验室开发前沿技术;②引入AI优化设计与生产;③构建绿色供应链体系。市场洞察:据Yole数据,2025年先进封装基板市场规模将达200亿美元,年复合增长率15%。风险提示:技术迭代加速,需关注行业标准更新与客户需求变化。 上海打样PCB厂家报价

文章来源地址: http://dzyqj.m.chanpin818.com/pcbdlb/deta_26498847.html

免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的用户,本网对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。

[VIP第1年] 指数:3

[VIP第1年] 指数:3